이번 포스팅은 SDB, DDB에 관련한 내용입니다. 공정을 하시는 분들이라면 SDB, DDB에 관련된 내용을 많이 들어보셨을 거 같습니다. 참고한 논문은 아래와 같습니다.

① Single and Double Diffusion Breaks in 14nm FinFET and Beyond

해당 문헌에서는 SDB, DDB에 따른 LDE(Layout Dependent Effect)와 Tech가 고도화되면서 해당 공정에 대한 변화를 설명하고 있습니다. 먼저 간단하게 LDE의 개념과 SDB, DDB에 대해 설명하고 논문 Review를 진행하겠습니다.

1. Layout Dependent Effect (LDE)

Layout Dependent Effect는 반도체 소자의 배치나 형상이 소자의 동작 특성에 미치는 영향을 설명합니다. 이는 소자의 설계가 일정 영역에 집중되거나 특정 구조로 배열되면, 전기적 성능이나 신뢰성에 영향을 줄 수 있다는 것을 의미합니다. 예를 들어, 트랜지스터의 채널 길이나 소자 간의 간격 등이 소자의 동작에 중요한 역할을 하며, 이를 설계 단계에서 고려하지 않으면 소자의 성능이 저하될 수 있습니다.

LDE는 다양한 형태 및 종류로 나타납니다. 가장 대표적으로 Short Channel Effect (SCE)가 있습니다. Gate Length에 따라서 성능과 특성이 달라지기 때문에 LDE로 분류할 수 있습니다. 이외에도 Latch-up도 LDE와 연관되어 있습니다. 만약 Body Bias가 가해지는 Tab 영역이 멀리 있다면 IR Drop에 따라 Latch-up이 유발될 수 있습니다. 이런 LDE를 개선하기 위해서는 먼저 Design Rule에 추가하여 설계부터 LDE를 고려한 설계가 필요합니다.

2. Single, Double Diffusion Break (SDB, DDB)

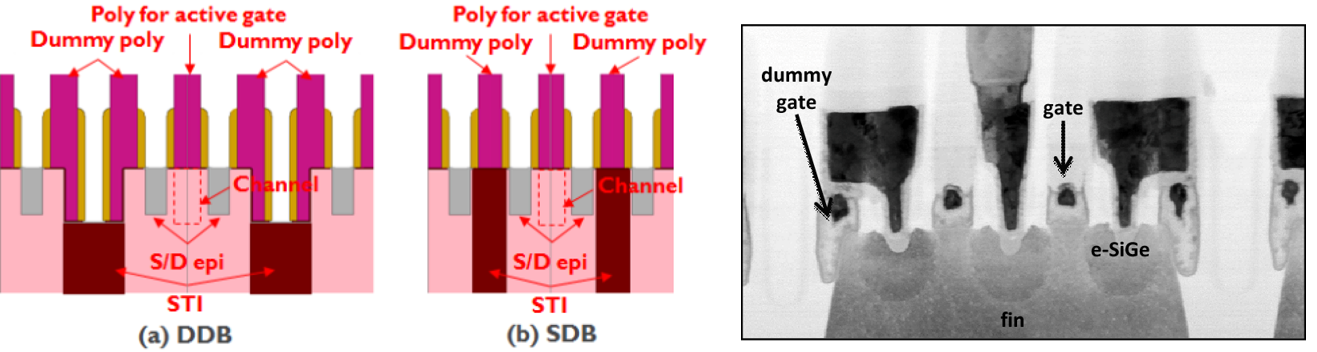

Diffusion Break는 인접한 소스와 드레인 사이에 트렌치를 형성해 트랜지스터를 분리하는 기술입니다. Cell과 Cell을 Isolation 시키기 위해, Tr과 Tr을 분리하기 위해 필요합니다. 기존에는 두 개의 더미 게이트 사이를 분리하는 Double Diffusion Break(DDB)가 일반적으로 사용되었습니다. 하지만 Samsung 14nm 공정에서 하나의 Dummy Gate 만을 분리하는 SDB(Single Diffusion Break)를 도입했습니다. 이를 통해 Chip 면적을 감소시킬 수 있었습니다.

SDB, DDB 또한 Layout Dependent Effect을 유발하는 공정 중 하나이며 Tech 고도화가 되면서 불량 개선을 위해 공정 또한 변해가고 있습니다. 크게 LDE와 공정 변화 순으로 Review 하도록 하겠습니다.

1. Introduction

SDB와 DDB는 CMOS 소자 간, Cell 간 Isolation 시키는 공정입니다. SDB와 DDB의 차이는 Isolation 시키는 면적의 차이입니다. DDB는 1CPP의 Length로 Isolation 시키고 양 끝에 Dummy Poly가 형성되게 되며, SDB는 1 Gate Length 만큼 Isolation 시키고 그 위에 Dummy Poly가 형성되게 됩니다.

2. SDB, DDB Layout Dependent Effect

SDB와 DDB는 LDE를 유발하는 Layout 중 하나입니다. 가장 주요하게 변하는 인자는 DDB와 Transistor 간의 거리에 따른 Channel Stress, Strain 변화입니다. 해당 문헌에서는 DDB와 가까운 3개의 Tr의 Channel Strain을 분석하였습니다.

해당 실험에서 N, PMOS 모두 DDB(STI)와 거리가 가까울수록 작은 Elastic Stiffness를 가지게 되어 Channel Strain이 감소하였습니다. 멀어질수록 Strain은 증가하게 되고 LOD3 부터 Saturation되는 양상을 보이게 됩니다. Channel Strain의 변화는 Drain Current로 이어지게 됩니다. DDB와 거리가 가까울소록 Drain Current는 감소하는 경향을 보이게 됩니다. 즉 SDB, DDB와의 거리에 따라 Tr 특성이 달라지는 LDE가 발생합니다.

3. SDB, DDB 발전 방향

기존에는 DDB를 적용하였지만 FinFET에서 Die 면적을 줄이기 위해 SDB를 많이 적용하고 있습니다. 하지만 SDB 적용에 따라 Mis-align 관련한 불량이 많이 발생하고 있습니다. Gate와 SDB간 간격이 일정하지 않으면 Source/Drain 형성 시 제대로 형성되지 못하여 EPI Volume이 감소하는 불량이 발생하고 있습니다. 또한 Contact 형성 시 충분한 Contact Area를 만들 수 없어 저항이 증가하게 됩니다.

해당 불량을 개선하기 위해 Self-aligned SDB라는 공정이 도입됩니다. 기존 SDB는 Fin 형성 이후 진행되었다면 SA-SDB는 Gate를 형성하고 SDB가 진행됩니다. 즉 기존에는 SDB Photo 공정 진행 시 Align을 맞출 구조가 없었지만, Gate를 형성하고 진행하는 SA-SDB는 Gate라는 Align 기준점이 생기게되어 Overlay가 개선되게 됩니다.

결론 및 의견

논문에서는 DDB와 거리가 가까울수록 Stress가 감소하는 LDE에 대해 기술하였습니다. 하지만 DDB에 어떤 물질을 채우는지, 어떤 공정을 쓰는지에 따라 Stress가 증가하는 LDE가 발생할 수 있습니다. 따라서 이 논문을 통해 얻어갈 수 있는 것은 SDB, DDB에 따른 LDE 발생이라고 생각됩니다.

Chip이 작아지면서 SDB에서 SA-SDB로 변화하고 있습니다. SA-SDB로 변화하면서 수율은 개선될 수 있지만 여전히 Layout Dependent Effect는 남아있습니다. 이를 개선하기 위해 나온 컨셉은 Electric SDB 입니다. Vdd를 공급하는 Power Line을 PMOS Gate에 연결하고, Vss를 공급하는 Power Line을 NMOS Gate에 연결하면 Transistor가 Off 상태로 유지됩니다. 물리적으로 Breakdown을 해주지 않기 때문에 LDE에서 벗어날 수 있습니다.

하지만 Transistor가 Off 상태라고 해도 미세전류는 흐르기 때문에 leakage나 Breakdown Voltage 측면에서 열화가 있습니다. 따라서 이러한 부분들을 고려해서 Physical / Electric SDB를 소자에 적용해야 합니다.

'논문 Review > Device & Process' 카테고리의 다른 글

| Gate-All-Around (GAA) 구조에서의 Body Effect 및 SS 특성 (0) | 2025.01.30 |

|---|---|

| [논문 Review] Gate to S/D Overlap Capacitance 영향 (0) | 2024.11.24 |

| SiGe Channel 및 Stress에 따른 PMOS 소자 특성 변화 (0) | 2024.11.03 |

| Parasitic Capacitance 종류 및 형성 과정 (0) | 2024.10.06 |

| [논문 Review] FinFET Fin Scaling에 따른 소자 특성 변화 (0) | 2024.09.29 |